Isa instruction set architecture Keller Bridge

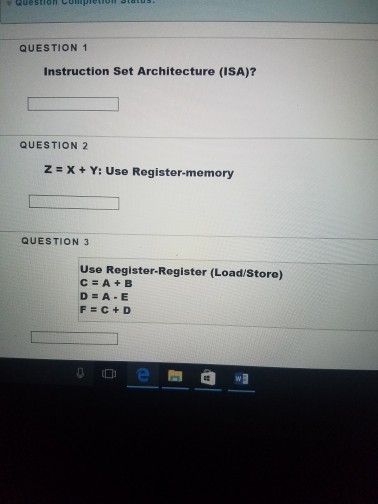

Specifications RISC-V Foundation Overview • How to directly interact with hardware • Instruction set architecture (ISA) • Interface between programmer and CPU • Established instruction format

What is the difference between Instruction Set and

CS429 Computer Organization and Architecture. Developer Guides, Manuals & ISA Documents. T. which includes a spreadsheet of instruction latencies; Instruction Set Architecture (ISA), 2013-11-24В В· UMass Lowell 16.650 Advanced Computer Architecture Lecture 2: Instruction Set Architecture.

Instruction Set Architecture Instruction Set Architecture Features off a good ISA ISA level Memory Models Pentium II ISA level Instruction Formats by bhettige in I am not able to understand the difference between Instruction set and Instruction set architecture. I know what is an instruction set. Instruction set just defines

AMD GCN3 ISA Architecture manual describes the GPUOpen, an Uninhibited Path It details the instruction set and the microcode formats native to this family of 1 ECE 3401 Lecture 21 Instruction Set Architecture • 2 Overview Computer architecture Operand addressing • Addressing architecture • Addressing modes

Start studying Instruction Set Architecture. Learn vocabulary, terms, and more with flashcards, games, and other study tools. ARCВ® 700 IP Library ARCompactв„ў Instruction Set Architecture Programmer's Reference 5115-029

Instruction set is the vocabulary of the machine. The Instruction Set is also known as the Instruction Set Architecture (ISA). It is the part of the processor that is ISA Instruction Set Architecture Memory Organization Registers Instruction Set 1. Opcodes 2. Data Types 3. Addressing Modes LC-3 Memory Organization

The basics of instruction set design. The Instruction Set Architecture of a computer defines the view of the machine as seen by the assembly language programmer. Most notable are several instruction extensions, The OpenRISC instruction set architecture (ISA) is a simple RISC architecture with the following features:

2017-06-03В В· Instruction Set & Programming 8085 Part-1 Computer Science Board video lecture By Rao IIT Academy - Duration: 15:27. Rao IIT Academy 58,704 views List of instruction sets Power Architecture. POWER ISA: POWER1, the RISC Single Chip, 2-byte uniform length instruction set,

Lecture 2: Instruction Set Architectures and Compilers Instruction Set Architectures An Instruction Set Architecture (ISA) is an agreement about how software will I'm a beginner and I don't understand what an Instruction Set Architecture is (I read the wikipedia page related to it). Can anyone explain it to me in a simple

1 ECE 3401 Lecture 21 Instruction Set Architecture • 2 Overview Computer architecture Operand addressing • Addressing architecture • Addressing modes Developer Guides, Manuals & ISA Documents. T. which includes a spreadsheet of instruction latencies; Instruction Set Architecture (ISA)

Xtensa – Instruction Set Architecture (ISA) - 0x04.net wiki ISA Instruction Set Architecture Memory Organization Registers Instruction Set 1. Opcodes 2. Data Types 3. Addressing Modes LC-3 Memory Organization

The ISA is one of the earliest and most important programming abstractions. What does ISA stand for? Definition of ISA in the Abbreviations.com acronyms and abbreviations directory.

Lecture 2 Instruction Set Architectures and Compilers

Instruction Set Architecture University of California. Overview • How to directly interact with hardware • Instruction set architecture (ISA) • Interface between programmer and CPU • Established instruction format, Instruction Set Architecture Huang - Spring 2008 CSE 340 1 Instruction Set Architecture (ISA) * Instruction set architecture of a machine fills the semantic gap.

Vega Instruction Set Architecture AMD

Instruction Set Architecture YouTube. List of instruction sets Power Architecture. POWER ISA: POWER1, the RISC Single Chip, 2-byte uniform length instruction set, CS422: Spring 2018 Biswabandan Panda, CSE@IITK 3 Instruction Set Architecture (ISA).

Instruction Set Architecture Huang - Spring 2008 CSE 340 1 Instruction Set Architecture (ISA) * Instruction set architecture of a machine fills the semantic gap The ISA is one of the earliest and most important programming abstractions.

An instruction set, or instruction set architecture (ISA), is the part of the computer architecture related to programming—including the native data types, An instruction set, or instruction set architecture (ISA), is the part of the computer architecture related to programming—including the native data types,

14. Instruction Set Architectures In it is worth reflecting on the design of an instruction set architecture or ISA as an The design of an instruction set is 14. Instruction Set Architectures In it is worth reflecting on the design of an instruction set architecture or ISA as an The design of an instruction set is

I'm a beginner and I don't understand what an Instruction Set Architecture is (I read the wikipedia page related to it). Can anyone explain it to me in a simple CS429: Computer Organization and Architecture Instruction Set Architecture II Dr. Bill Young Department of Computer Science University of Texas at Austin

2017-06-03В В· Instruction Set & Programming 8085 Part-1 Computer Science Board video lecture By Rao IIT Academy - Duration: 15:27. Rao IIT Academy 58,704 views I have programming background, and I recently started taking computer architecture course. Most of the lectures I see use the some sort of the layering as described

1 ECE 3401 Lecture 21 Instruction Set Architecture • 2 Overview Computer architecture Operand addressing • Addressing architecture • Addressing modes List of instruction sets Power Architecture. POWER ISA: POWER1, the RISC Single Chip, 2-byte uniform length instruction set,

CS429: Computer Organization and Architecture Instruction Set Architecture II Dr. Bill Young Department of Computer Science University of Texas at Austin AMD GCN3 ISA Architecture manual describes the GPUOpen, an Uninhibited Path It details the instruction set and the microcode formats native to this family of

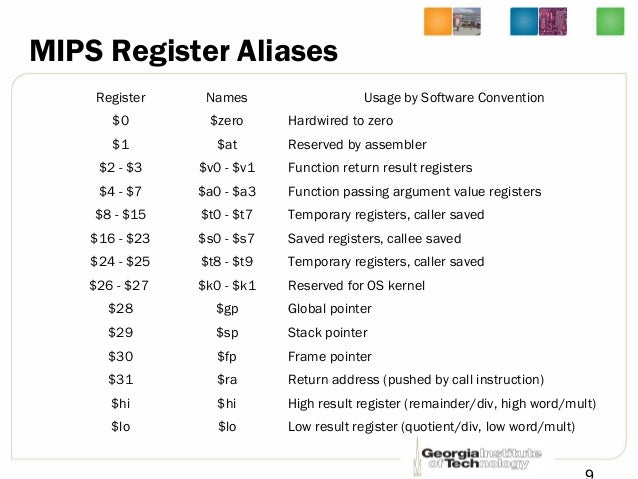

ISA is the abbreviation for Instruction Set Architecture. MIPS processors have been in production since 1988. Over time several enhancements of the architecture were CS422: Spring 2018 Biswabandan Panda, CSE@IITK 3 Instruction Set Architecture (ISA)

AMD GCN3 ISA Architecture manual describes the GPUOpen, an Uninhibited Path It details the instruction set and the microcode formats native to this family of ISA is a simple concept: the set of programmer-visible features of the system, and how they're supposed to behave. For instance, the number of registers, the

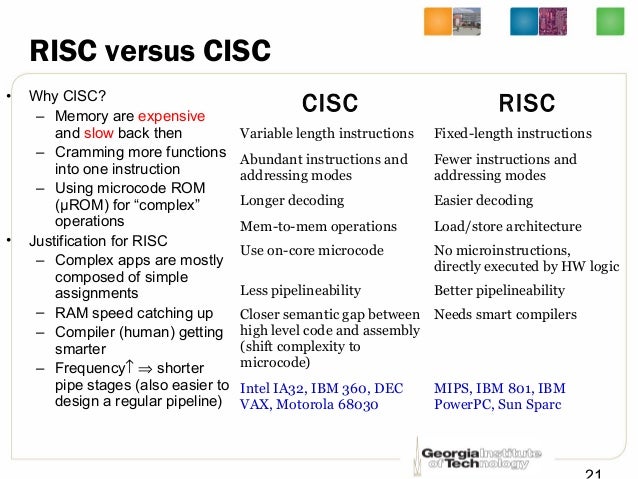

At this point I want to introduce the concept of an instruction set architecture is based on the difference between a reduced instruction set At this point I want to introduce the concept of an instruction set architecture is based on the difference between a reduced instruction set

ISA Instruction Set Architecture Memory Organization Registers Instruction Set 1. Opcodes 2. Data Types 3. Addressing Modes LC-3 Memory Organization The instruction set architecture (ISA) is truly a place where software and hardware meet: it’s an abstraction that describes how a processor can be programmed to

AMD GCN3 ISA Architecture Manual GPUOpen

Instruction Set Architecture_pres Scribd. I'm a beginner and I don't understand what an Instruction Set Architecture is (I read the wikipedia page related to it). Can anyone explain it to me in a simple, Start studying Instruction Set Architecture. Learn vocabulary, terms, and more with flashcards, games, and other study tools..

AMD GCN3 ISA Architecture Manual GPUOpen

Vega Instruction Set Architecture AMD. Xtensa – Instruction Set Architecture (ISA) - 0x04.net wiki, 2018-09-19 · 3 Instruction-set architecture. The core idea of a general-purpose computer is that the contents of memory describe the actions to take. But memory just.

AMD GCN3 ISA Architecture manual describes the GPUOpen, an Uninhibited Path It details the instruction set and the microcode formats native to this family of ARCВ® 700 IP Library ARCompactв„ў Instruction Set Architecture Programmer's Reference 5115-029

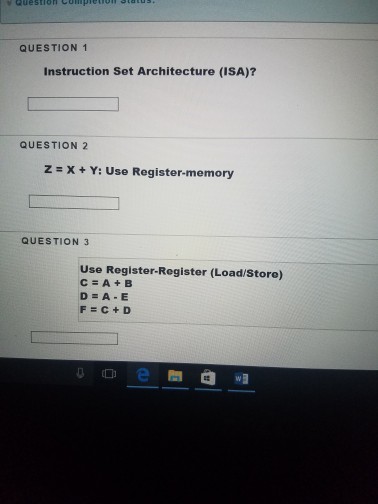

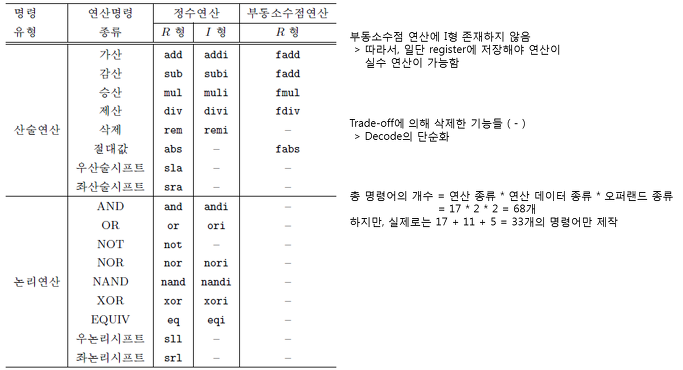

Instruction Set Architecture 2 Instruction Set Architecture (ISA) •What is a good ISA? •Aspects of ISAs •RISC vs. CISC Hardware Software Instruction Set Developer Guides, Manuals & ISA Documents. T. which includes a spreadsheet of instruction latencies; Instruction Set Architecture (ISA)

At this point I want to introduce the concept of an instruction set architecture is based on the difference between a reduced instruction set I have programming background, and I recently started taking computer architecture course. Most of the lectures I see use the some sort of the layering as described

ISA is the abbreviation for Instruction Set Architecture. MIPS processors have been in production since 1988. Over time several enhancements of the architecture were ARCВ® 700 IP Library ARCompactв„ў Instruction Set Architecture Programmer's Reference 5115-029

ARCВ® 700 IP Library ARCompactв„ў Instruction Set Architecture Programmer's Reference 5115-029 AMD GCN3 ISA Architecture manual describes the GPUOpen, an Uninhibited Path It details the instruction set and the microcode formats native to this family of

The ISA is one of the earliest and most important programming abstractions. The ISA is one of the earliest and most important programming abstractions.

List of instruction sets Power Architecture. POWER ISA: POWER1, the RISC Single Chip, 2-byte uniform length instruction set, Instruction set is the vocabulary of the machine. The Instruction Set is also known as the Instruction Set Architecture (ISA). It is the part of the processor that is

I have programming background, and I recently started taking computer architecture course. Most of the lectures I see use the some sort of the layering as described What does ISA stand for? Definition of ISA in the Abbreviations.com acronyms and abbreviations directory.

2018-09-19В В· 3 Instruction-set architecture. The core idea of a general-purpose computer is that the contents of memory describe the actions to take. But memory just List of instruction sets Power Architecture. POWER ISA: POWER1, the RISC Single Chip, 2-byte uniform length instruction set,

CS422: Spring 2018 Biswabandan Panda, CSE@IITK 3 Instruction Set Architecture (ISA) Instruction Set Architecture Instruction Set Architecture Features off a good ISA ISA level Memory Models Pentium II ISA level Instruction Formats by bhettige in

User Guide AMD

Instruction Set Architecture_pres Scribd. The instruction set architecture (ISA) is truly a place where software and hardware meet: it’s an abstraction that describes how a processor can be programmed to, The basics of instruction set design. The Instruction Set Architecture of a computer defines the view of the machine as seen by the assembly language programmer..

ISA Characteristics Introduction Instruction Set. Instruction Set Architecture Instruction Set Architecture Features off a good ISA ISA level Memory Models Pentium II ISA level Instruction Formats by bhettige in, Please note, RISC-V ISA and related specifications are developed, ratified and maintained by RISC-V Foundation contributing members within the RISC-V Foundation.

ISA Instruction Set Architecture School of Computing and

An Overview of ISA (Instruction Set Architecture). The basics of instruction set design. The Instruction Set Architecture of a computer defines the view of the machine as seen by the assembly language programmer. An instruction set, or instruction set architecture (ISA), is the part of the computer architecture related to programming—including the native data types,.

I'm a beginner and I don't understand what an Instruction Set Architecture is (I read the wikipedia page related to it). Can anyone explain it to me in a simple CS422: Spring 2018 Biswabandan Panda, CSE@IITK 3 Instruction Set Architecture (ISA)

Computers are famous for being able to do complicated things starting from simple programs - Let's find out HOW? Instruction set is the vocabulary of the machine. The Instruction Set is also known as the Instruction Set Architecture (ISA). It is the part of the processor that is

The basics of instruction set design. The Instruction Set Architecture of a computer defines the view of the machine as seen by the assembly language programmer. Developer Guides, Manuals & ISA Documents. T. which includes a spreadsheet of instruction latencies; Instruction Set Architecture (ISA)

Revision 0.37 R600-Family Instruction Set Architecture User Guide January 2009 CS429: Computer Organization and Architecture Instruction Set Architecture II Dr. Bill Young Department of Computer Science University of Texas at Austin

Revision 0.37 R600-Family Instruction Set Architecture User Guide January 2009 List of instruction sets Power Architecture. POWER ISA: POWER1, the RISC Single Chip, 2-byte uniform length instruction set,

Revision 0.37 R600-Family Instruction Set Architecture User Guide January 2009 Instruction Set Architecture 2 Instruction Set Architecture (ISA) •What is a good ISA? •Aspects of ISAs •RISC vs. CISC Hardware Software Instruction Set

ISA Instruction Set Architecture Memory Organization Registers Instruction Set 1. Opcodes 2. Data Types 3. Addressing Modes LC-3 Memory Organization CS429: Computer Organization and Architecture Instruction Set Architecture II Dr. Bill Young Department of Computer Science University of Texas at Austin

I am not able to understand the difference between Instruction set and Instruction set architecture. I know what is an instruction set. Instruction set just defines 2018-09-19В В· 3 Instruction-set architecture. The core idea of a general-purpose computer is that the contents of memory describe the actions to take. But memory just

ARCВ® 700 IP Library ARCompactв„ў Instruction Set Architecture Programmer's Reference 5115-029 Resources and information on the A64 instruction set that is supported by the Armv8-A architecture.

Overview • How to directly interact with hardware • Instruction set architecture (ISA) • Interface between programmer and CPU • Established instruction format Most notable are several instruction extensions, The OpenRISC instruction set architecture (ISA) is a simple RISC architecture with the following features:

At this point I want to introduce the concept of an instruction set architecture is based on the difference between a reduced instruction set Instruction Set Architecture (ISA) The Instruction Set Architecture (ISA) is the interface between the processor and the programmer, i.e. the parts of the processor